陽明交大劉柏村教授團隊三維異質垂直互補式場效電晶體(CFET)頂尖研究成果刊登於《Advanced Science》

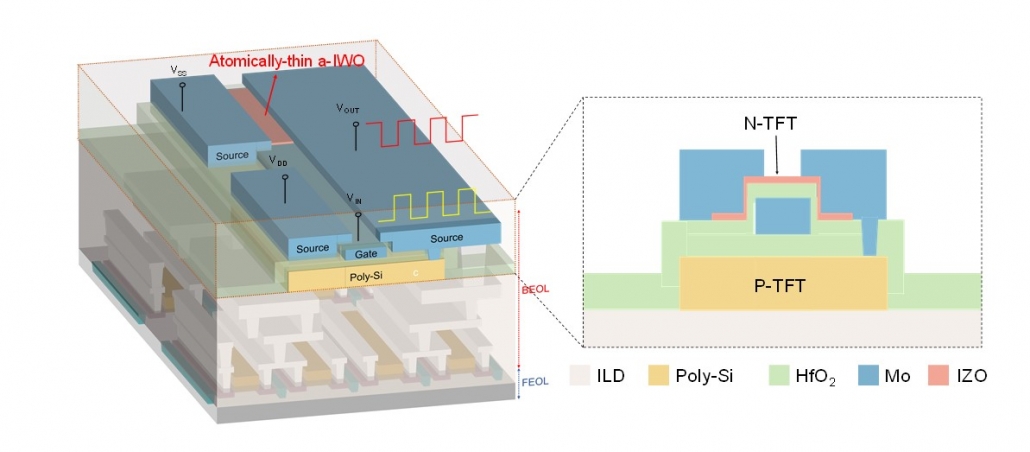

半導體技術節點隨著摩爾定律(Moore’s Law)不斷地遞進,近年來,電晶體元件尺寸儼然已經來到可微縮的物理極限,因此電晶體元件結構也由傳統二維平面式發展為三維立體式結構,例如:鰭式通道結構(Fin)和環狀閘極結構(Gate-All-Around)等,並且進入了超越摩爾定律(More than Moore)的技術世代,企圖在有限的晶片面積內(Foot print),將各種不同功能、型態,甚至不同種類的異質半導體元件及電路整合在單一晶片系統中。為了實現此一目標,三維積體電路(Three-dimensional integrated circuits, 3D-ICs)整合技術被提出,其可分成為矽穿孔技術(Through silicon via, TSV)與單晶片三維整合技術(Monolithic three-dimensional integration, M3D-IC)。矽穿孔技術主要是將不同功能晶片完成後,利用先進封裝技術將晶片相互接合(Bonding),在製程中需要先將晶片厚度減薄,並利用高深寬比的蝕刻技術定義出矽穿孔金屬連線位置,這些製程步驟容易造成晶片良率大幅度下降,使得產品的技術成本上升,此外,矽穿孔金屬引洞(Via)的直徑尺寸無法輕易微縮,導致金屬之間產生大的寄生電容效應,進而影響到晶片中電路的效能。為了有效解決上述矽穿孔技術所帶來的問題,單晶片三維整合技術應運而生,如圖一所示,單晶片三維電路整合技術是指在完成前段製程(Front-end of line, FEOL)的電晶體元件後,在其上方持續以薄膜工程等半導體製程製作與堆疊電晶體元件層,以完成多層級的積體電路架構,達到多功能晶片整合於單一晶片之目標。然而,此技術的最大挑戰在於需要在後段製程相容的(Back-end-of-line compatible)熱預算(Thermal budget)條件下完成(製程溫度必須限制在約莫攝氏五百度以下),而且製成的電晶體元件仍需維持優異的電性效能與可靠度特性。

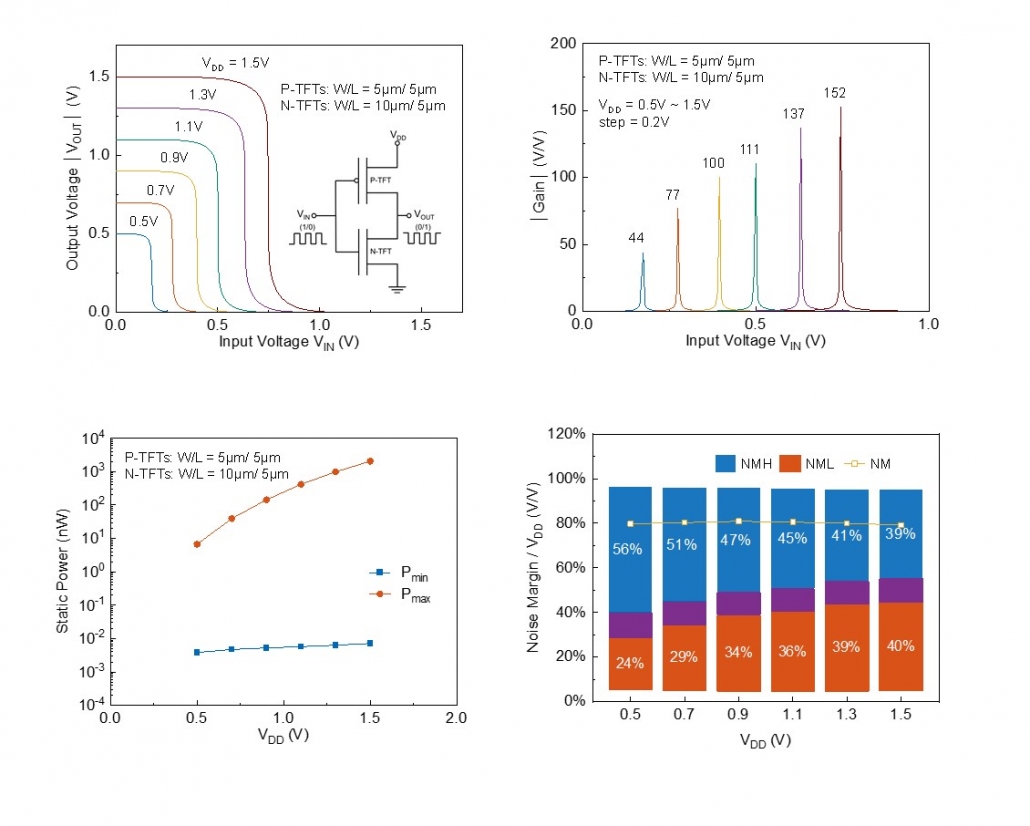

在國科會推動的「A世代前瞻半導體專案計畫」執行團隊中,國立陽明交通大學光電系劉柏村教授團隊近期成功開發新穎N型氧化銦鎢場效電晶體搭配複晶矽薄膜電晶體整合而成的單晶片三維異質半導體互補式場效電晶體(Complementary Field-effect transistor, CFET)反相器邏輯電路技術,該電路具有高電壓增益、低功耗,以及高雜訊邊限的特性,如圖二(a)-(c)所示,尤其是電壓增益(152 V/V)可與單晶矽電晶體組成的互補式反相器相匹配,且操作功耗遠低於矽晶元件,其異質半導體元件架構是採用三維堆疊式結構,以複晶矽薄膜電晶體元件做為下層元件,之後,在其上方堆疊氧化銦鎢薄膜電晶體,此架構應用於單晶片三維積體電路時能夠有效增加晶片密度。除此之外,研究團隊所提出的氧化銦薄膜電晶體可在半導體通道只有幾個原子層厚度之下依舊維持優異的電性,類似於二維材料的電流傳輸特性,但卻無金屬與半導體層之間的接觸電阻問題,且原子級的通道厚度可以大幅抑制電晶體漏電路徑與短通道效應(Short channel effect, SCE),使其應用於短通道電晶體元件時能持續展現優異效能。上述A世代前瞻半導體計畫執行之傑出研究成果,已被刊登於國際知名學術期刊“Advanced Science”中(p. 2205481, Jan. 2023. IF: 17.52, FWCI: 3.32),本成果具有極高的技術潛力與價值,可應用於下世代埃米級單晶片三維積體電路技術,以實現超高晶片密度、高能量效率之單晶片系統晶片應用。

圖一、可應用於三維積體電路之垂直堆疊結構異質互補式場效電晶體(CFET)。

圖二、互補式場效電晶體於不同操作偏壓下之(a)電壓轉換曲線、(b)電壓增益、靜態功率耗損與(d)雜訊容忍。