執行現況與成果

先進製程之高密度三維蝕刻孔電阻式記憶體元件與陣列設計開發

主持人

共同主持人

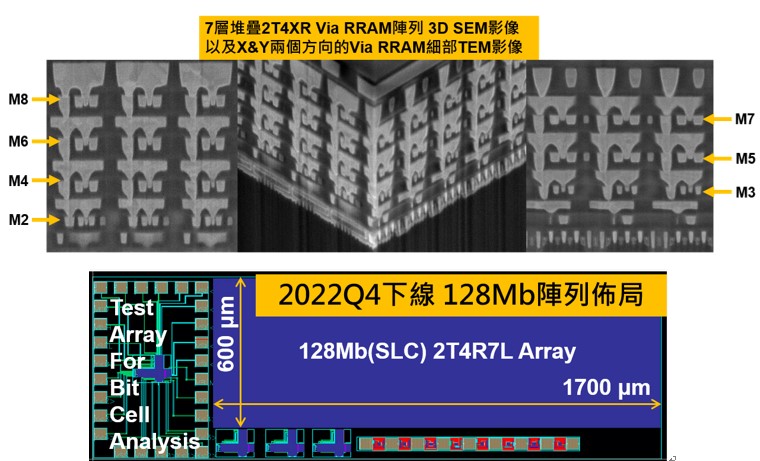

- 建立基於導電細絲現象之RRAM元件模型,包含電流-導電細絲間距公式、物理參數的定義以及高低阻態模型擬合量測數據,模擬電阻在轉態的過程中其流通電流的變化曲線。高密度三維堆疊記憶體陣列在7奈米製程達到8層堆疊,預計可將密度提升至0.6Gb/mm2。

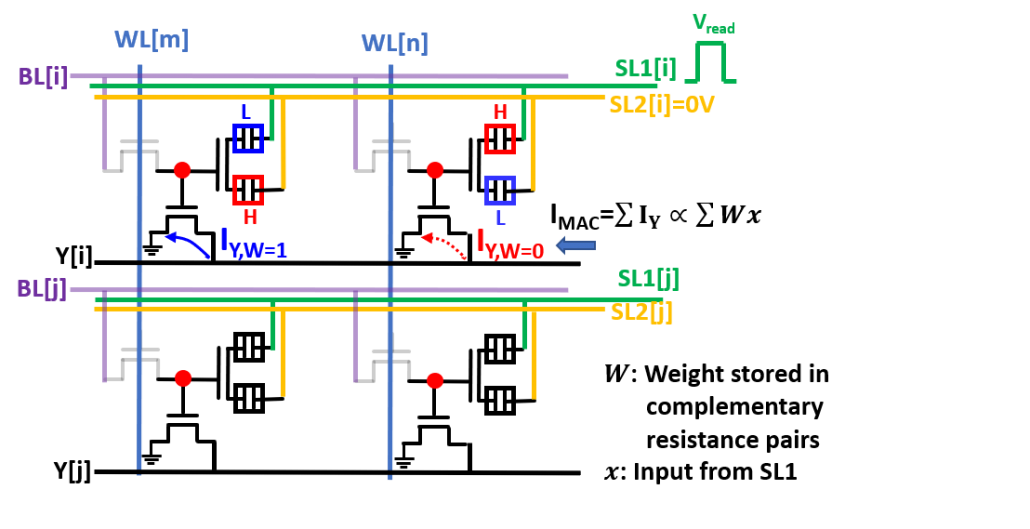

- 計畫目標為三維通孔電阻式高速類神經網路晶片應用,設計記憶體架構完成記憶體內運算,並配合製程下線完成實作。計畫預計在2024Q3下線1T3L/1T2L Via-RRAM邏輯閘,並同時實現基於N7技術節點的FINDRRAM類神經元以及 1kbits類神經網路陣列。Via-RRAM邏輯閘包含1T2L和1T3L結構,結構顯示其在邏輯運算中的應用潛力,並通過高低阻值累積分布圖展示了其性能穩定性和可靠性。此外,設計 1T3L Via-RRAM邏輯閘的操作流程,包括清除、寫入和讀取等步驟。總體而言,計畫在記憶體內運算和類神經元陣列技術方面取得了顯著的進展,相關成果發表於國際期刊IEEE Transactions on Electron Devices (TED)。

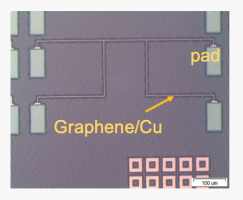

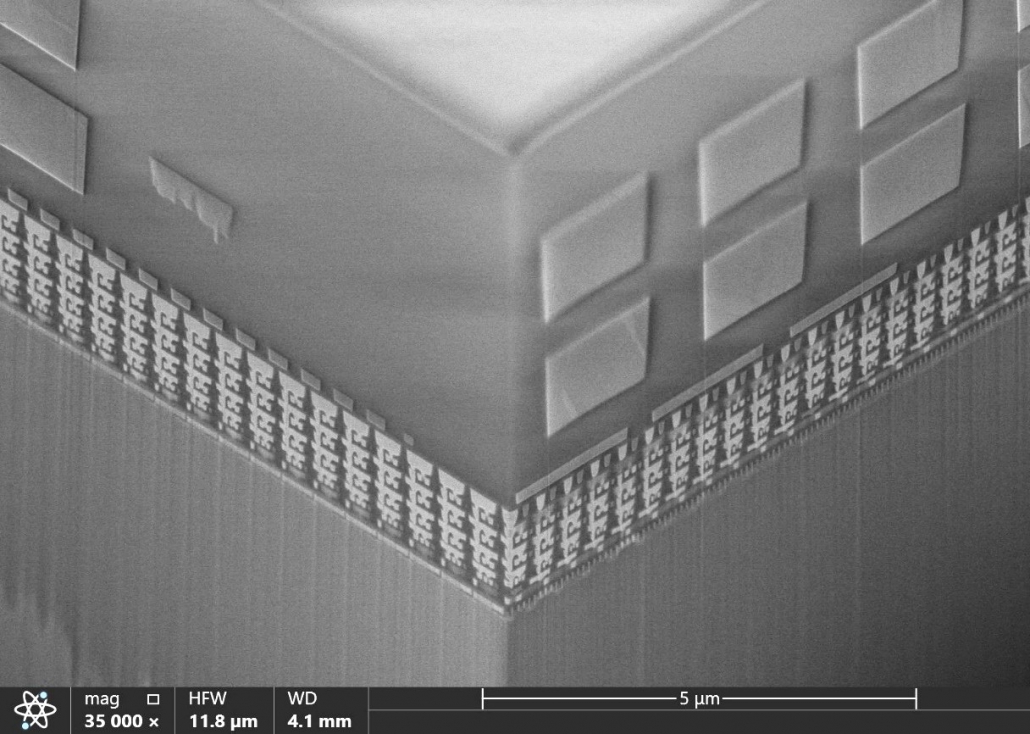

- 計畫目標為開發小線寬高導電度石墨烯/銅導線低溫成長技術,全程以攝氏400度低溫環境於N16晶片銅導線成長石墨烯之參數,銅線線寬為45 nm~800 nm。低溫成長石墨烯後,利用拉曼頻譜分析證實通入碳源之C-H鍵可以裂解並且在銅線上成長石墨烯。計畫所研究之石墨烯與其相關元件成果陸續發表於國際期刊,包括Advanced Optical Materials、Macromolecular Rapid Communications、Optics Express、IEEE Electron Device Letters等期刊。在創新技術研發期間,每年有五位碩博士生投入執行計畫,培育之科學和技術人才畢業後投入半導體產業,促進前瞻技術和產品的創新發展。

實際驗證在16nm技術節點中,在與此CMOS鰭式電晶體邏輯製程完全相容下,以7層金屬層堆疊的三維通孔電阻式記憶體2T4XR元件來建構下線晶片密度(SLC)達到0.13 Gb/mm2的128Mb實體陣列。透過電性分析確認堆疊共計8層的雙位元通孔電阻式記憶體特性,採用鰭式電晶體控制的電阻轉換操作和足夠的讀取視窗;同時透過電流限制的操作,使通孔電阻式記憶體具備二位元多層次儲存的特性,進一步提升記憶體密度。

新型雙位元鎖存器式記憶體內運算元件將高密度電阻式記憶體結合數位邏輯閘”鎖存器”概念實現於奈米級CMOS前端邏輯製程,將互補非揮發性資料儲存於雙位元HKMG電阻對之中,資料的寫入與清除皆可於40奈秒(ns)內達成,單一位元的資料讀取可於5奈秒內完成,有效減少了43%的能耗,儲存資料在元件內直接進行邏輯運算,利用一輸出電晶體的放大特性有效提升了讀取視窗,實現超過800倍之開關電流訊號比。並展現多階儲存單元特性,應用於類神經運算晶片之多位元的類比乘積累加運算,實現高密度權重組態儲存。

以化學氣相沈積法與電漿輔助方式全程400℃在銅導線上成長石墨烯,透過調整氣體流量、升溫參數與電漿參數,控制石墨烯的厚度、電性與品質。已驗證16nm技術節點晶片寬度0.4~10 µm銅導線上石墨烯的成長技術,樣品製備完成後以拉曼頻譜確認銅導線上的材料為石墨烯,並分析不同參數下成長的石墨烯品質;已證實石墨烯/銅薄膜的導電度高於純銅,已在16nm技術節點平台製作知晶片上成長石墨烯/銅導線結構,期望實現低電阻石墨烯/銅複合導線於16nm技術節點晶片。