執行現況與成果

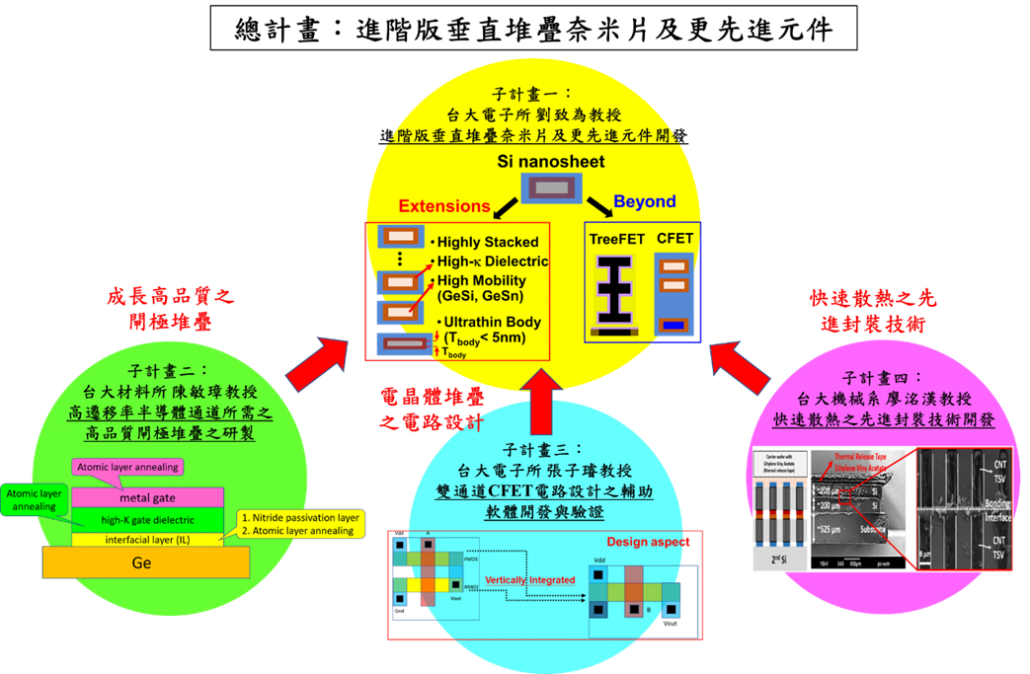

進階版垂直堆疊奈米片及更先進元件

主持人

共同主持人

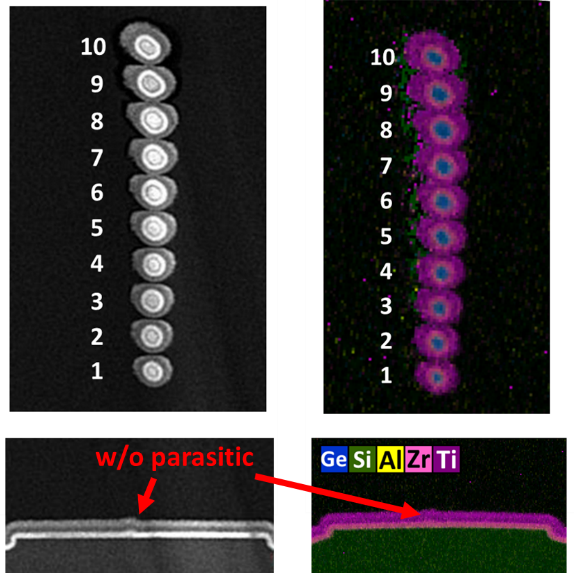

奈米線閘極環繞式場效電晶體有良好的短通道控制。高堆疊的奈米線通道可以在相同佔地面積下提供更大的電晶體驅動電流。本研究團隊持續增加通道堆疊數目,透過優化多層數鍺矽/鍺磊晶層與合適之蝕刻選擇比等向性濕式蝕刻製程,成功製備出十六層堆疊鍺矽奈米線電晶體,其電晶體擁有紀錄之驅動電流。為了進一步提升電晶體效能,利用兩步驟之濕式蝕刻製程,成功製備無寄生通道之十二層堆疊鍺矽奈米線電晶體,其電晶體有效降低次臨界擺幅與漏電流。本研究成果已發表於國際期刊Nature/Communications Engineering,足見此成果之重要性與傑出程度。

本研究團隊基於單晶片互補式堆疊電晶體結構開發經驗,進一步優化製程,達成世界首顆單晶片堆疊整合異質鍺錫與鍺矽奈米片之互補式堆疊電晶體。透過磊晶成長底層鍺矽奈米片電晶體之通道層、中間之犧牲層以及上層鍺錫奈米片電晶體之通道層,過程中不需要晶圓接合即可達成異質鍺錫與鍺矽通道之整合。藉由鍺錫與鍺矽通道之間的能帶偏移,僅使用單一種金屬功函數閘極堆疊即完成閾值電壓匹配的反相器,無須採用高深寬比雙金屬功函數閘極堆疊之複雜製程。相關成果已發表於2023 IEDM國際研討會以及國際期刊IEEE Transactions on Electron Devices,並與業界(imec, intel, CEA-Leti, Samsung, and tsmc)同台發表,可見此成果之

重要突破性與傑出程度。

極薄通道電晶體具有良好的次臨界擺幅、高開關電流比。而受應變鍺錫材料具有比鍺較高之電洞遷移率,可承受極薄通道下的遷移率損失。在享有極薄通道電晶體好處的同時有良好的驅動電流。首先藉由磊晶成長四奈米的鍺錫磊晶層,再利用高選擇比的蝕刻,製備出通道厚度降至約兩奈米之鍺錫極薄通道電晶體。藉由量子侷限效應擴大材料能帶,可達到高源汲極崩潰電壓。使電晶體在邏輯上有良好的特性,也可以應用在高電壓的通訊上。本研究成果已發表於國際期刊IEEE Electron Device Letters。

在高層數堆疊鍺矽通道方面,接續2021 VLSI的研究成果,優化蝕刻關鍵製程,去除寄生通道,並成功製備6層堆疊鍺矽通道,得到更低的次臨界擺幅(80mV/dec)及更高的開關電流比(1.5E5),在鍺/鍺矽三維N型電晶體,VOV=VDS=0.5V時,達到每通道堆疊驅動電流120μA(每單位通道寬度驅動電流4600μA/μm),為當時的世界紀錄,此研究成果發表論文於2022 VLSI-TSA,並榮獲Best Student Paper Award (最佳學生論文獎)。為了持續增加電晶體的驅動電流,以增加通道堆疊數目為首要目標,成功製備10層堆疊鍺矽通道,其驅動電流達到140μA(6500μA/μm),其研究成果發表論文於2022 SISC。透過磊晶與濕式蝕刻兩大模組相互優化,已成功製備16層堆疊鍺矽通道,其驅動電流達到190μA(9400μA/μm),其研究成果已投稿至Nature communications engineering。

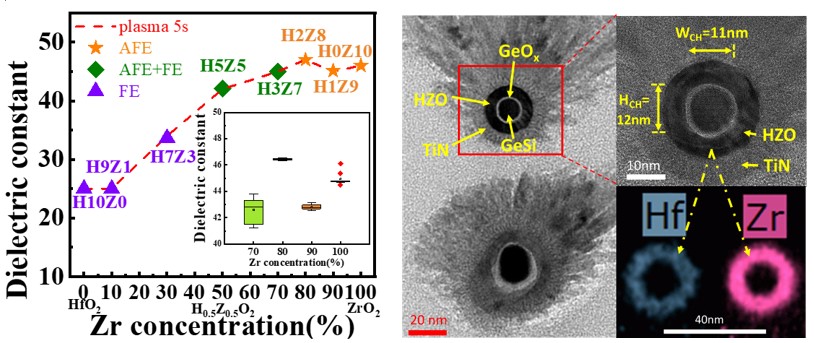

本團隊經由有系統的研究HfxZryO2高介電常數材料調變氧缺陷及Zr在HfxZryO2之濃度,優化在Hf0.2Zr0.8O2得到介電常數之峰值為47,約為HfO2介電常數之2倍,並將高介電常數材料成功整合於2層堆疊高遷移率鍺矽三維N型電晶體,VOV=VDS=0.5V時,達到每通道堆疊驅動電流67μA(每單位周長驅動電流740μA/μm),其研究成果發表論文於2022 IEEE EDL國際期刊。

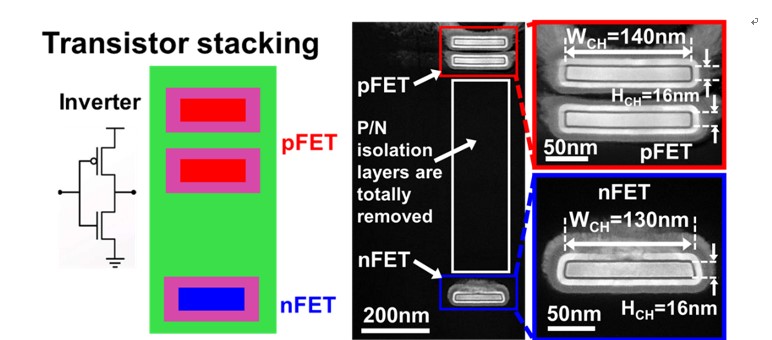

團隊開發用將於0.5nm (5Å)世代的CFET電晶體結構,將nFET與pFET奈米片電晶體進行垂直方向的堆疊並且組成反相器結構,相較於通道的垂直堆疊可以更進一步減少反相器單元的占地面積(最多可減少至原先面積的一半),可提升單位面積內的電晶體數目,增加運算效能。其中以high mobility GeSi channel作為CFET結構之nFET與pFET通道所使用,並且採用P/N junction isolation作為堆疊n/pFET間之電性隔絕,能夠取代dielectric isolation並有效化簡元件製作流程,CFET構成之反相器於400oC PMA過後可達成9.6V/V之voltage gain。相關成果已發表於2022 IEDM國際研討會。