執行現況與成果

高效能記憶體增強型神經網路之AI架構與電路開發

主持人

共同主持人

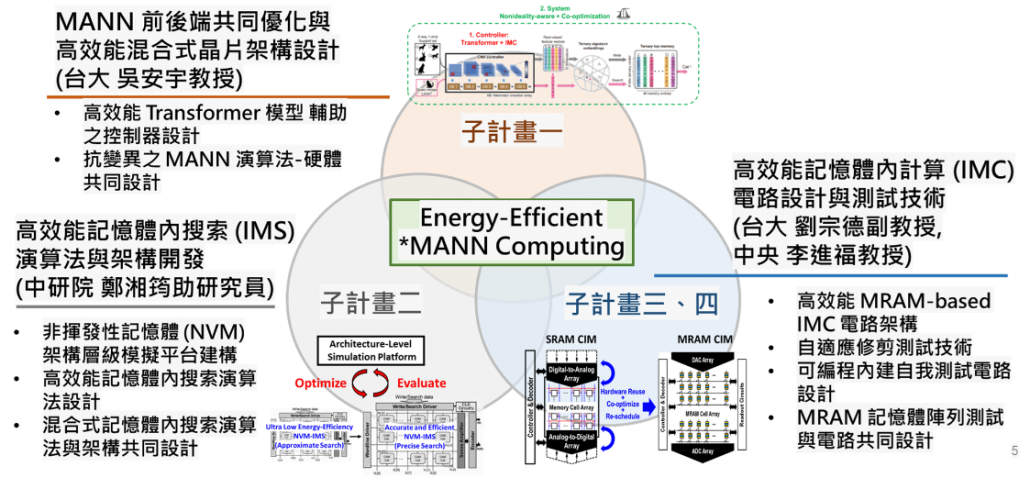

為導入台灣半導體技術於未來AI系統,本團隊聚焦於低訓練複雜度的記憶體增強型神經網路 (MANN) 研究,並進行電路、架構與演算法層面之設計技術協同優化,以開發高效能AI運算系統。本團隊的主要技術包括: 1) 基於非揮發性記憶體的高效能混合式記憶體內搜索架構,2) 基於MRAM元件的高效能記憶體內運算電路與測試技術,3) 適用於MANN的混合式AI運算架構設計。為此,我們提出三項子計畫進行技術開發,以達成下一代高效能AI運算系統的目標。

在本A世代半導體計畫架構下,子計畫一將著重於MANN前後端軟硬體協同優化與高效能混合式AI加速訓練晶片設計,提供完整針對MANN前端基於記憶體內運算 (IMC) 之資料特徵萃取之解決方案。子計畫二將著重於NVM-based高效能記憶體內搜索 (IMS) 電路中的演算法與架構開發,提供完整針對MANN後端向量相似度搜索之NVM-IMS的解決方案。子計畫三、四將著重於MRAM-based高效能記憶體內運算的電路設計與測試技術開發,提供完整針對MANN前端運算之MRAM-CIM的解決方案。

高能效稀疏Transformer處理器晶片

近年來,基於Transformer的AI模型在各領域取得了巨大成功。吳安宇教授團隊基於演算法-硬體共同設計,以台積電28奈米製程實作高能效稀疏Transformer處理器晶片,主要創意與貢獻如下:(1) 在多頭注意力機制中,將8-bit運算拆解為4-bit,動態篩選冗餘運算,減少92%運算量,降低27.1%能源消耗。(2) 使用查找表及迭代長除法器優化Softmax函數,降低60.8%硬體面積及27.2%的能源消耗。(3) 針對稀疏矩陣運算,採用一大核+三小核架構,提升4.3倍的運算吞吐量並降低33.6%的能源消耗。

此晶片在NLP、CV領域的代表性模型 (GPT-2, ViT) 上驗證,可在<1%準確率損失的情況下減少92%的運算量,量測結果最低功率消耗為3.82W,達到最高64.5 TOPS/W 的能源效率,相較於先前文獻提升1.3至5.75倍。此晶片可支援不同序列長度的Transformer模型,能夠應對未來快速更迭的各式人工智慧應用需求,保持高效能與高準確率!

記憶體增強型神經網絡 (MANN)

記憶體增強型神經網絡 (MANN) 在少樣本學習 (FSL) 中取得顯著成效。本團隊提出了一種高能效向量相似度搜索架構,透過優化搜索方式與編碼模組提升系統能效。主要創意與貢獻如下:

1.提出限縮L∞距離搜索(Banded L∞, L∞ b),跳過冗餘搜索迭代,減少平均搜索次數1.94倍至3.39倍。

2.優化範圍編碼(Range Encoding),支援範圍對範圍的搜索,減少40%至68%的編碼長度。

3. 提出基於距離的訓練機制,提高L∞搜索準確度3.25%至4.76%,並減少搜索迭代次數1.22倍至1.31倍。

在標準FSL數據集上的實驗結果顯示,相較於先前的EX-TCAM的方法,能效提高了9.35倍至11.84倍,準確率提高了2.95%至4.69%,此論文發表於DATE 2024。

STT-MRAM讀取電路通常會設計多個可修剪參考電阻,並於量產測試時透過修剪測試來克服製成變異造成的良率損失。為克服修剪測試非常耗時的問題,我們提出(1)Parallel-check trimming技術(PCTT): 透過同時配置不同讀取電阻於對應讀取電路,來達到快速找到適當參考電阻,對比二元搜尋修剪測試技術,可降低測試時間41%,此技術已發表於IEEE ETS。另外,為提高STT-MRAM讀取可靠度,我們提出(2)Fault-aware error correction code (FA-ECC): 當ECC偵測到讀取錯誤時,FA-ECC可以分辨錯誤讀取瑕疵或讀取干擾瑕疵,並透過調整參考電阻修復錯誤讀取瑕疵,此技術可於相同可靠度下可提升3.15x使用壽命,此技術已發表於IEEE ITC-Asia。

Parasitic-free stacked nanowires結合3D MTJ技術

劉致為教授團隊將高層數堆疊高遷移率通道之nanowires成果發表於 2021 年超大型積體電路技術研討會 (VLSI Symposia on Technology),並且獲選為Highlight Paper,其驅動電流為鍺/鍺矽三維電晶體之世界紀錄 (>4000 mA/mm @ VOV=VDS=0.5V) [1]。此成果榮獲國際頂尖期刊Nature Electronics報導於Research Highlight,也刊登於臺大校訊與NTU HIGHLIGHTS。

3D MTJ技術

劉致為教授團隊將自旋軌道力矩磁性穿隧接面成果發表於 2021 年超大型積體電路技術研討會 (VLSI Symposia on Technology) ,並且獲選為Highlight Paper,透過用鎢做多層擴散阻擋層,可以達到400C的熱穩定性,且使用鉈鎢自旋軌道力矩通道可提供高自旋霍爾角度,可以同時增加元件蝕刻的process window,並且可利用自旋轉移力矩 (STT) 達成零磁場轉換 [2]。

高效能及高運算解析度之記憶體內計算電路系統技術表現

劉宗德教授團隊透過解析Computing-in-memory (CIM) 之構成與運作機制之後發現,Memory Array和數位與類比轉換溝通界面之間存在許多冗餘的電路操作。因此子計畫二提出一個Unified CIM Network設計方法,利用協同設計與最佳化思維來設計新型的CIM Cell,該新型CIM Cell共集成了四種功能,1) 基本的Memory Read/Write, 2) 乘法-累加運算(Multiply-Accumulate, MAC),3) ADC的核心功能,以及4) 參考電壓 (Vref) 生成與SAR電容切換。透過此技術,CIM可免除使用獨立且成本高昂的ADC來將Bit‑Line上的MAC結果轉換成數位碼,取而帶之的是將ADC的運算拆解並融入Memory Array之中,藉此避免了大量的冗餘能量與面積消耗,最終提升CIM Macro層級達到383 TOPS/W的能源效率,此研究成果已在頂級期刊IEEE Journal of Solid-State Circuits (JSSC) 期刊發表 [3]。

高能源效率AI運算架構與演算法開發

吳安宇教授團隊所發表論文Trainable Energy-aware Pruning (T-EAP),榮獲2022 年IEEE AICAS (AI for Circuits and Systems) 最佳學生論文獎 (Best Student Paper Award) [4],本技術使用Georgia Tech團隊所開發的DNN+NeuroSim平台模擬的能源資訊,並利用此能耗資訊讓DNN在剪枝(pruning)的過程當中,針對能耗較大的權重進行剪枝,以達文獻中最佳準確率-能耗之效能。以T-EAP為基礎,本團隊進一步提出E-UPQ: Energy-Aware Unified Pruning-Quantization Framework,可訓練的參數在壓縮過程中進行可微分的剪枝/量化(quantization)共同搜索。相較於完整精度模型,本團隊所提出之CIM能源覺察壓縮技術使ResNet-18及VGG-16模型在CIM平台上運行之能源效率 (TOPS/W) 提升4倍,並已發表於 IEEE Journal on Emerging and Selected Topics in Circuits and Systems [5]。

Reference

[1] Y. -C. Liu et al., “Highly Stacked GeSi Nanosheets and Nanowires by Low-Temperature Epitaxy and Wet Etching,” in IEEE Transactions on Electron Devices, vol. 68, no. 12, pp. 6599-6604, 2021.

[2] Y. -J. Tsou et al., “Thermally Robust Perpendicular SOT-MTJ Memory Cells With STT-Assisted Field-Free Switching,” in IEEE Transactions on Electron Devices, vol. 68, no. 12, pp. 6623-6628, 2021. |

[3] C. -Y. Yao, T. -Y. Wu, H. -C. Liang, Y. -K. Chen and T. -T. Liu, “A Fully Bit-Flexible Computation in Memory Macro Using Multi-Functional Computing Bit Cell and Embedded Input Sparsity Sensing,” in IEEE Journal of Solid-State Circuits, 2023.

[4] C. -Y. Chang, Y. -C. Chuang, K. -C. Chou and A. -Y. Wu, “T-EAP: Trainable Energy-Aware Pruning for NVM-based Computing-in-Memory Architecture,” IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), pp. 78-81, 2022.

[5] C. -Y. Chang, K. -C. Chou, Y. -C. Chuang and A. -Y. Wu, “E-UPQ: Energy-Aware Unified Pruning-Quantization Framework for CIM Architecture,” in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 13, no. 1, pp. 21-32, 2023.