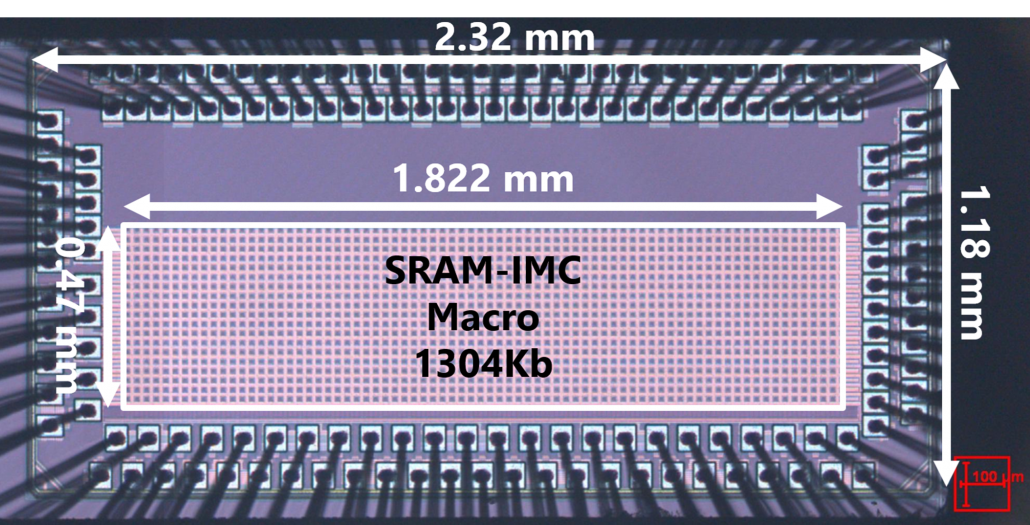

本計畫將結合應用演算法、硬體架構與低功耗電路技術、及電路設計與佈局實現之跨領域技術,達到設計之最佳化。其中硬體加速器將採用以SRAM為基礎的記憶體內運算單元,解決傳統范紐曼架構下的記憶牆能耗問題,並結合脈衝式神經網路的仿生運算演算法,利用其高稀疏性計算與脈衝輸出入特性,降低系統能耗。此外,將發展電路運算核心單元可重組架構,以滿足卷積式網路與脈衝式網路不同應用需求。同時發展次臨界電壓操作與晶片內元件變異感知技術,進行分散式電壓補償及特性的正規化。為了支援此新型計算架構之高能效需求,我們也開發考慮電路變異的混訊電路最佳化及自動化佈局工具,協助本計畫提高運算能力,並結合變異強健模型,系統化解決電路變異問題,達到低功耗操作之目標,同時保證仿生運算的正確性。