執行現況與成果

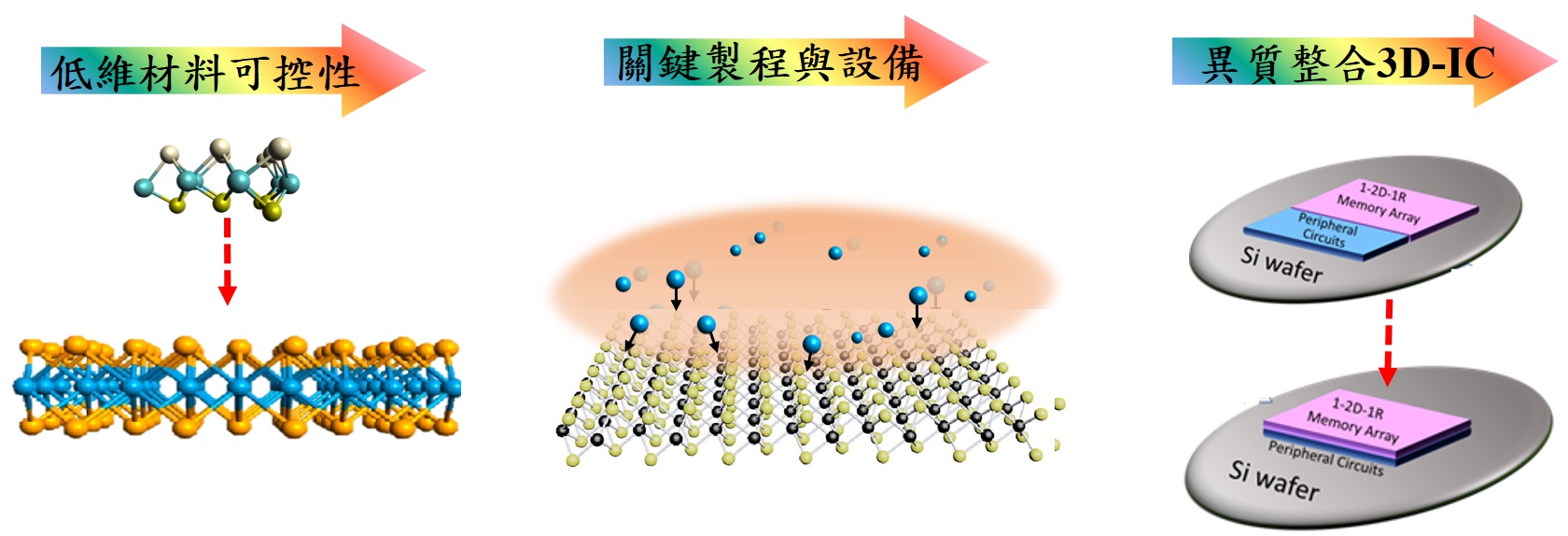

低維度新穎材料、晶圓級製程與關鍵技術整合於建構前瞻半導體元件之

研究

主持人

共同主持人

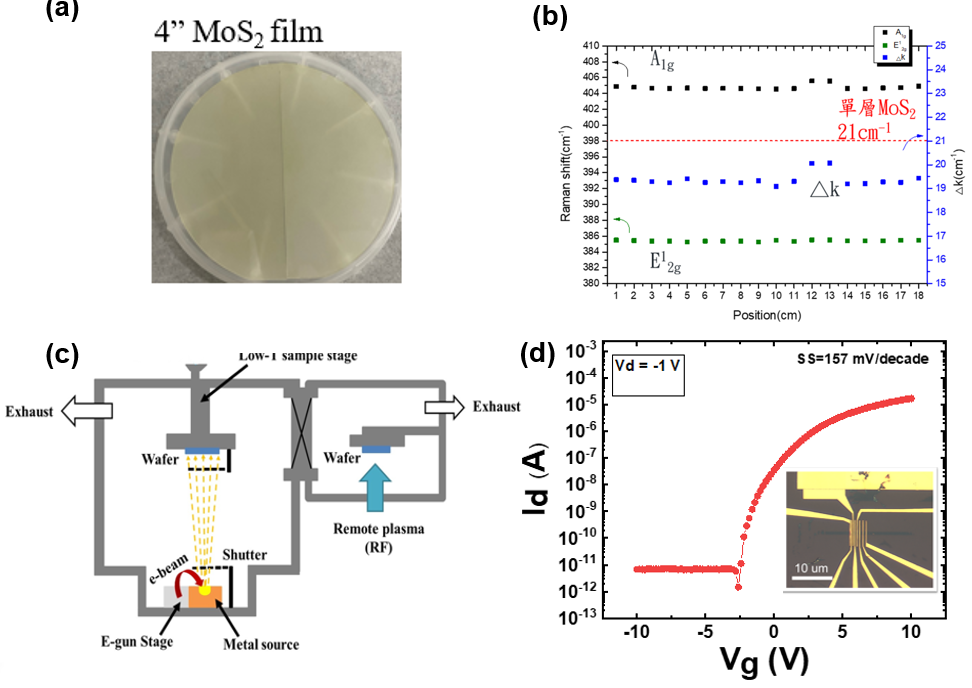

1. 團隊成功建立一可低溫合成大面積合成MoS2生長製程與設備,可於低溫<550℃進行晶圓級單層MoS2生長,此成果已完成技轉。

此外,建立一個獨特的原子級操控於低損傷改質平台,可達到原子級低損傷接面改質/原子層剝除,有效的提升元件效能,包含導通電流、載子遷移率達一個數量極提升,此技術已獲台灣專利1件、申請美國專利3件審查中。

圖1. (a)-(b) 電漿輔助於低溫前驅物生長單層MoS2連續膜。(c)-(d) 低損傷臨場改質/原子層剝除(ALE)技術於二維材料接面改質並提升元件效能

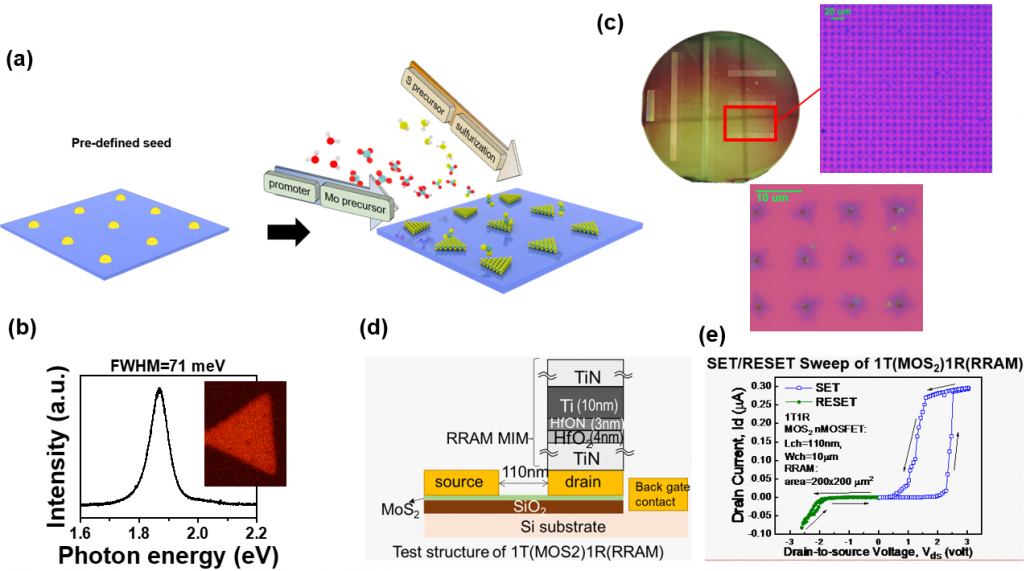

2. 成功開發一可相容於BEOL之生長技術並可直接應用於元件製程。此技術以新型前驅物合併促進物的使用,輔以點位(seeding)基板設計(4″ SiO2基板),可直接於SiO2氧化物基板上進行選擇性單晶低溫生長控制。此外,也成功以MOCVD於400度低溫完成可垂直整合堆疊於製作1T-1R RRAM元件進行驗證,其具備良好之穩定性voltage < 3 V; PGM_Current < 1 μA/μm; endurance >106; retention: 10 years @100°C。成果發表於2D-TMD 2023研討會。

圖2. (a)-(c)新型前驅物和促進物於低溫可控性單晶合成生長技術。(d)-(e)以MOCVD製作相容於BEOL(400oC)的1T (MoS2 nMOSFET)-1R (RRAM MIM)元件。

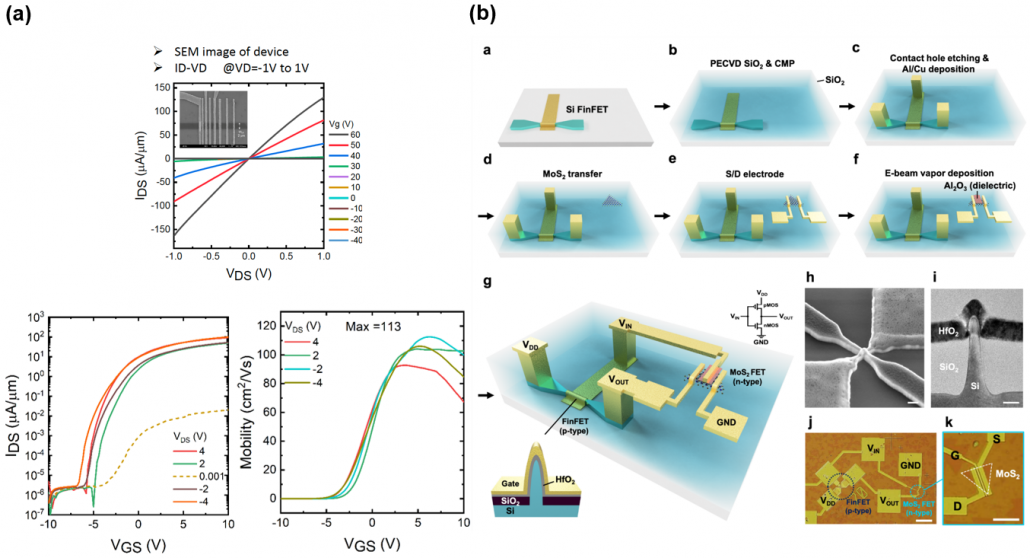

3. 本團隊進行金屬選擇與優化,有效的降低金屬接觸阻抗,獲得超低接觸電阻95 ohm mm,導通電流密度達 90 mA/mm (VDS=1),電子遷移率達 113 cm2/Vs。並提出一套二維材料與半導體元件之積層式三維整合製程技術(整合矽與後段製程於功能性元件),利用高遷移率與高驅動電流的前段P-type Si-based FinFET整合於後段低溫n-type MoS2 FET,製作功能性邏輯電路,可滿足後段整合之製程要求。3D inverter中兩個電晶體的開關電流比和開啟電流顯示相似的水平,展示其在CMOS整合具有高的相容性能。此外,反相器亦呈現明顯的信號反轉,及最大電壓增益達到約38。此項成果已發表於npj 2D Mater Appl 7, 9 (2023)

圖3. (a) 介面改質於超低金屬接觸,(b) 建構矽與後段製程相容的二維材料之功能性元件