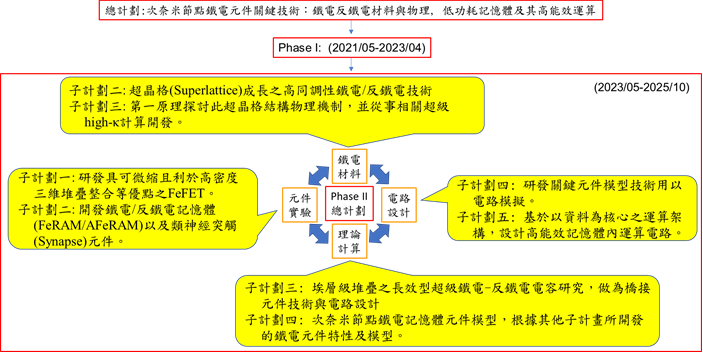

執行現況與成果

次奈米節點鐵電電晶體關鍵技術:

鐵電反鐵電材料與物理, 低功耗記憶體及其高能效運算

主持人

共同主持人

Analog-Based Synapse of Double Superlattice-HfZrO2 Ferroelectric-FETs Toward Energy-Efficient Accelerator

本研究著眼於類神經運算之突觸(synapse)加速器,提出使用雙層超晶格(superlattice, SL)成長模式的HZO,以達鐵電相之勻質與調和性。實驗結果顯示出優秀的線性交互連續增強(向上)和抑制(向下)電導線性度(αp/αd = -0.85/0.63),其中方均根電壓3V相較於國際團隊可有效降低。此外,針對SL-HZO通過幾何相位分析(GPA)驗證鐵電正交相(orthorhombic-phase)可達75-79%,與傳統固態溶解法(solid-solution, SS)之62-64%相比明顯提高。雙層鐵電HZO (DHZO)具非均一性晶粒尺寸,進而有效分散矯頑場(Ec)分佈,有助於鐵電晶域(domain)翻轉電場分散,利於多階與Analog Synapse操作。本研究展示有8個臨界電壓之多階數據存儲且具間隙等大等優點,有助於TLC(三位元記憶晶胞)開發,其錯誤率為1.9×10-4,與SS-DHZO相比有~100倍改善。本研究發表於IEEE Transactions on Materials for Electron Devices (2024)。

A New Approach for Reconfigurable Multifunction Logic-in-Memory Using Complementary Ferroelectric-FET (CFeFET)

研究針對互補式鐵電電晶體(CFeFET)之n-FeFET及p-FeFET上下堆疊結構,探討其於數位式記憶體內運算之應用。本研究利用CFeFET中鐵電電晶體在enhancement mode及depletion mode來回切換,使其成為非揮發性的2對1多工器(MUX),可節省傳統路由開關(routing switch)的電晶體數目。而且,我們展現如何利用此2對1多工器的特性實現可重構式的“AND/OR/XOR”邏輯閘,且訊號完整度更高。本研究有助於未來以資料為核心之運算。發表於 IEEE Transactions on Electron Devices (2023八月)。

Robust Recovery Scheme for MFIS-FeFETs at Optimal Timing with

Prolonged Endurance

本研究首次探討MFIS FeFET恢復操作的最佳時機點,以得到最佳延長耐久度之操作,並與國際技術相比:(1) 操作過程幾乎無記憶窗口損耗(~ 0.02 %),(2) 所需恢復操作時間短(100ns),(3) 自動啟動恢復操作之設計。此成果有助於FeFET有效地延長操作耐久度,相關研究發表於國際頂尖會議IEDM (2023十二月)。

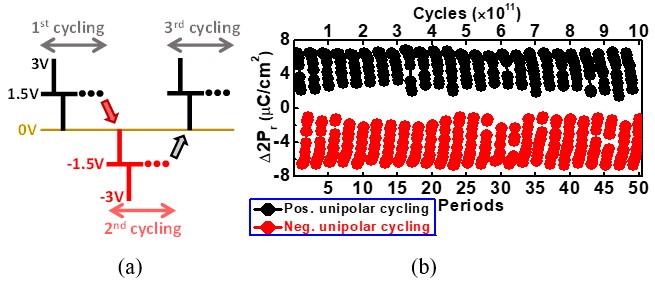

反鐵電技術與操作

反鐵電電容具有單極性操作且彼此的疲勞與漏電互相獨立特性,本團隊首創提出反向極性循環恢復(Opposite polarity cycling recovery, OPCR)於單極性交替循環操作,其中透過反向極性循環使氧空缺重新分布,使原先已疲勞的極化量與漏電可完整恢復至初始狀態,並且透過實際展示OPCR 50個週期,累積極化切換(polarization switching)至1012次,結果顯示極化量無衰退及完整恢復的特性,如圖一,此應用有機會解決現今記憶體耐用度的極限與瓶頸,將可提供未來嵌入式DRAM解決方案。相關研究成果已發表於2022 International Electron Devices Meeting (IEDM 32.5)與邀稿刊登至IEEE Transactions on Electron Devices (T-ED)。

(a) 反向極性循環恢復(Opposite polarity cycling recovery, OPCR)操作波型。(b) 反鐵電電容使用OPCR 50個週期,累積極化切換(polarization switching)至1012次。

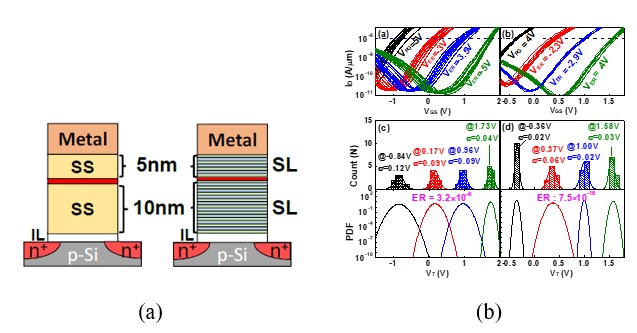

開發超晶格(Superlattice)成長技術及高鐵電相HZO

本團隊採用超晶格(Superlattice, SL)的鐵電氧化層沉積方式,以提高鐵電相率,並以此成長模式用於雙層鐵電結構,如圖二,增加多階記憶體之穩定度,SL相較於目前固態溶解法(solid-solution, SS),不只降低操作偏壓(VPG/ER=4V),同時具有極低的讀取錯誤率(error rate=7.5×10-16)與優異的耐用度特性(> 109次),並提供穩定的數據保持能力(>104s),此外,因SL具高鐵電相率優點,可提供鐵電層高同質性(homogenous),進一步將SL應用於三維立體電晶體結構,於尺寸微縮或立體結構上,可降低元件間的差異性(D2D variation)。以上研究結果已發表於2022 International Electron Devices Meeting(IEDM 36.6)。

(a) 使用SL及SS成長模式之雙層鐵電結構示意圖。(b) 4階記憶體操作,SL之穩定性於讀取錯誤率大幅優於SS。

關鍵反鐵電/鐵電模型技術

- 本團隊針對反鐵電/鐵電HZO,已建構出可描述其動態極化翻轉和頻率響應模型,並發表於IEDM 2021 (15.4) 。

- 本團隊已成功發展Fatigued HZO之反鐵電/鐵電動態翻轉模型並發表於IEDM 2022 (13.4)。

- 本團隊所發展之模型可用於未來反鐵電/鐵電記憶體電路模擬與設計。