執行現況與成果

三維嵌入式阻變閘非揮發性記憶體架構:

NOR及NAND的實現

主持人

共同主持人

協同研究人員

1TnR NOR RG-RAM(Resistive-Gate RAM) 結構電阻式記憶體的示範

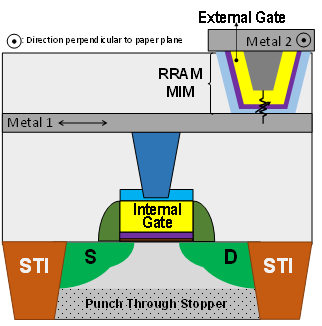

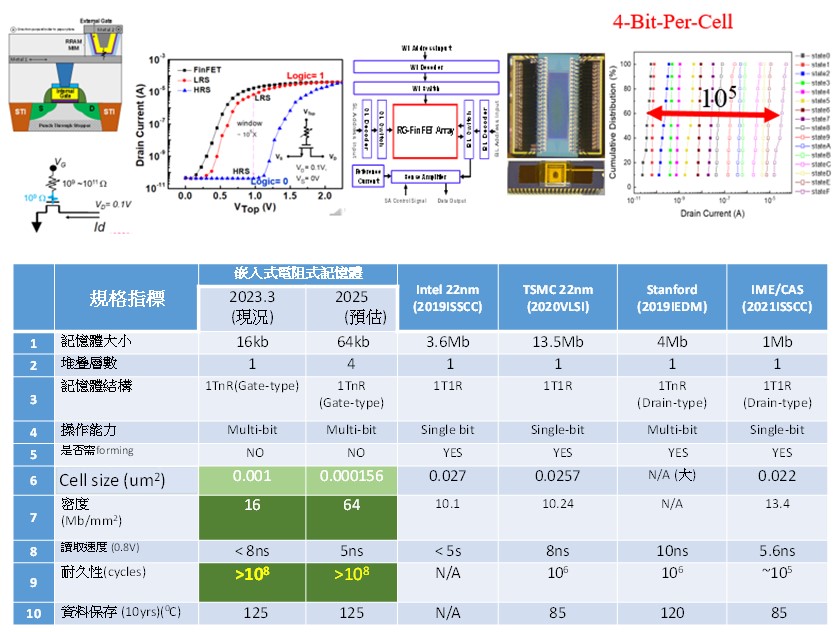

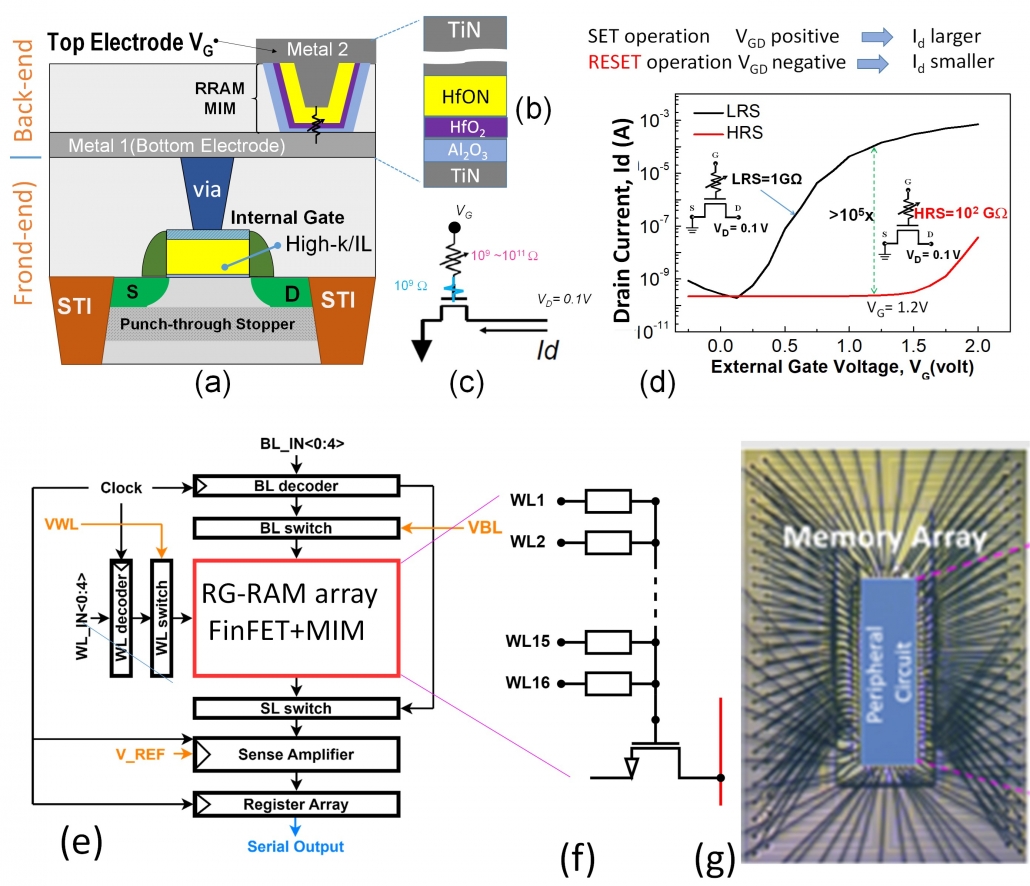

本計畫第一期已完成高效能1T1R FinFET製作平台,且整合成1kb的RRAM晶片與展示,因特有的gate-type 1T1R結構, 圖(a)-(d),可以凌駕現有各大廠及學研界的drain-type結構,適合發展高密度適用於28nm/16nm以及更先進尺寸的嵌入式記憶體。

近期吾等運用1TnR概念,順利完成NOR結構1T16R 1kbits的雛型, 圖(e)(f)(g)。它系運用自行製作的1k bits array FinFET平台, 配合周邊電路的設計及晶片製作(tsmc shuttle)來整合完成。整體而言,已完成的雛型具有下列優點: (1) 細胞元小,一個unit cell可以實現4-bit per cell共16 狀態的Multi-bit操作,具有寬廣window(105), 其他各大廠及學研界發表的drain-type結構僅有約10-100倍的window (不適合作Multi-bit操作), (2) 高速的操作program/read time分別為10nsec/12nsec。(3)記憶體的耐久性(10^8)優於台積電與Intel已量產的技術,(4) 本RG-RAM結構適合發展3D AND/NAND結構。

電阻式記憶體RG-RAM於AI Inference Accelerator的應用

本研究運用團隊於 [1]發表的1T1R RG-RAM為基礎,拓展到AI edge加速器的應用[2]。結合1T1R的TLC(Triple-Level Cell)多階操作以及處理器(NPU, Neuromorphic Processor Unit) 的設計,吾等以RG-RAM記憶體陣列做資料儲存及累加運算,並採用4核心的NPU處理器運算,運用降低位元數的訓練模型(Quantized training model),以現有資料庫(MNIST及CIFAR-10)來做運算仍可分別維持97.24% 及80.18%的準確度,達到運算效能40.6 TOPS/W,對於記憶體內運算CIM(Compute-In-Memory)的硬體設計及類神經網路之應用,極具參考價值。

- M. Y. Lee et al., “A World First QLC RRAM: Highly Reliable Resistive-Gate Flash with Record 108 Endurance and Excellent Retention,” in IEEE IRPS, March 27-30, 2023.

- Y. L. Lin, Y. R. Liu, T. C. Kao, M. Y. Lee, J. C. Guo, T. –H. Hou, and S. S. Chung, “An RRAM-Based 40.6 TOPS/W Energy-Efficient AI Inference Accelerator with Quad Neuromorphic-Processor-Unit for Highly Contrast Recognition,” IEEE VLSI-TSA, April 2024.

本文榮獲2024 IEEE VLSI-TSA Best Student Paper Award

FinFET-based Memory 於AI Inference Accelerator的應用

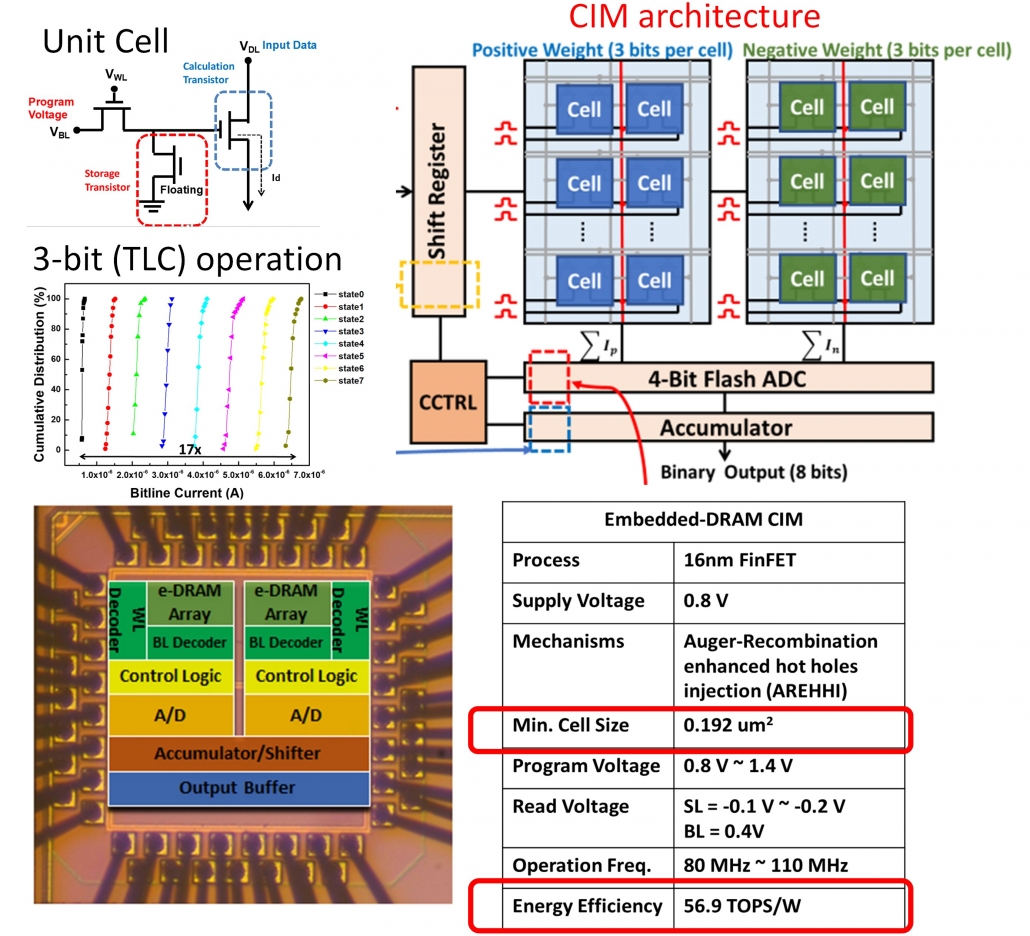

本研究團隊在2024年六月VLSI頂尖國際會議發表一項類比運算的記憶體,運用TLC的觀念,建構出CIM macro晶片,可用於AI edge運算的應用[1]。其原理是運用本團隊的創新發明,稱之為AREHHI(Auger recombination enhanced hot hole injection)物理操作機制。和前面主題2或大多數採用SRAM, DRAM的研究不同,本項設計採用簡單的方式來達到記憶體內運算。運用台積電16奈米平台且不需額外光罩,吾等設計出面積的2k bits運算記憶體單元,結合TLC(Triple-Level Cell)多階操作,提出全部使用FinFET(All FinFET-based)完成仿DRAM功能設計出操低電壓操作(0.8V-1.4V)的DRAM嵌入式記憶體(e-DRAM),具有高速(110MHz),高運算效能56.9TOPS/W及90.07%高準確度的記憶體設計(晶片面積0.192μm²),所建構的CIM架構,可以作為後續發展RG-RAM (1T1R或1T16R架構)於AI accelerator的平台,對類神經網路之發展具有參考價值。

- T. C. Kao et al., “An Ultra-low Voltage Auger-Recombination Enhanced Hot Hole Injection Scheme in Implementing a 3 Bits per Cell e-DRAM CIM Macro for Inference Accelerator,” IEEE VLSI, JFS 6.3, Hawaii, June 2024.

QLC (Quad Level Cell)- 世界上首創4 bit/cell電阻式記憶體

本計畫第一年已完成高效能FinFET製作平台,且整合成1kb的RRAM晶片與展示,因特有的gate-type 1T1R結構,可以凌駕現有各大廠及學研界的drain-type結構,適合發展高密度的垂直式結構。我們結合自行製作的1k bits array FinFET平台, 配合周邊電路的設計及晶片製作(TSRI shuttle),順利完成1T16R 1kbits的雛型。

該1kb的1T16R RRAM晶片雛型,可以讓1kb的設計提升到等效於16kb的設計容量。整體而言,這個完成的雛型具有下列優點: (1) 細胞元小,一個unit cell可以實現4-bit per cell共16 狀態的Multi-bit操作,具有寬廣window(2×105), 其他各大廠及學研界發表的drain-type結構僅有約10-100倍的window (不適合作Multi-bit操作), (2) 記憶體的耐久性(108)優於台積電與Intel量產的技術, (3) 資料保存特性可在125度C溫度下達到十年的可靠性 ,優於台積電與Intel量產的技術。

- Y. Lee, J. P. Wu, C. H. Liu, J. C. Guo, and S. S. Chung, “A World First QLC RRAM: Highly Reliable Resistive-Gate Flash with Record 108 Endurance and Excellent Retention,” in IEEE IRPS, March 27-30, 2023.

- E. R. Hsieh, K. T. Chen, P. Y. Chen, S. Wong, S. S. Chung, “A FORMing-Free HfO2/HfON-Based Resistive-Gate Metal–Oxide–Semiconductor Field-Effect-Transistor (RG-MOSFET) Nonvolatile Memory With 3-Bit-Per-Cell Storage Capability,” in IEEE Transactions on Electron Devices, vol. 68, no. 6, pp. 2699-2704, June 2021.

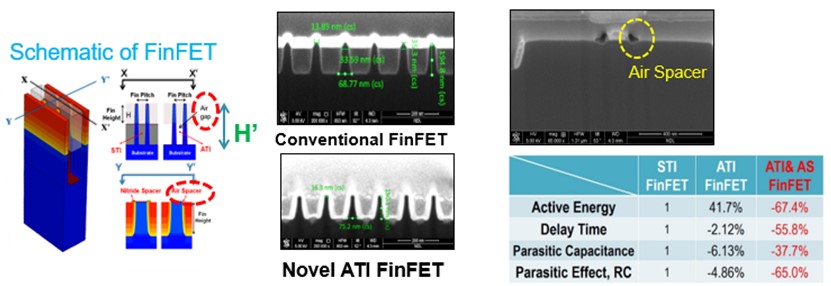

3nm FinFET電晶體的設計準則

本文針對團隊多年來發展的FinFET,建構一個可以達到3nm的設計準則。在此一設計上,FinFET採用可以增加Width folding的ATI(Active Trench Isolation)方式,增加ION電流,同時採用air-spacer以改善delay, 在整體的表現上,相較於傳統的FinFET結構,可以達到1.43倍的速度,功耗可以降低54%。同時,該製程甚為穩定,提供本計畫穩定的FinFET平台。其高效能電晶體製造技術,對半導體產業具實用價值。

- (Invited) S. S. Chung, et al., “The Extension of the FinFET Generation Towards Sub-3nm: The Strategy and Guidelines,” IEEE EDTM, March 5-9, Oita, Japan, 2022)

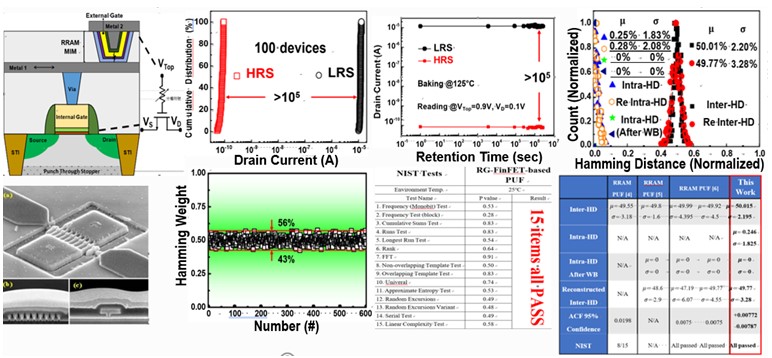

採用電阻式FinFET記憶體的物理不可複製功能函數(PUF)晶片

2022年9月於日本最大半導體會議SSDM的論文, The Demonstration of a Physical Unclonable Function (PUF) on a Resistive-Gate FinFET Memory,展示一個本計畫規劃完成的1kb RRAM晶片製作,且成功運用於PUF,入選為SSDM最佳論文候選。

本研究探索了阻變閘非揮發性記憶體於資訊安全方面的應用潛力,首次實作1kb的阻變閘記憶體組成的實體不可複製功能晶片(包含周邊電路),其結果顯示了非常良好的資安參數特性。(包含Intra-HD, Inter-HD, HW, Auto-correlation, NIST-Test等。)

- M. Y. Lee, T. J. Kao, Y. C. Lee, E. R. Hsieh, J. C. Guo, and S. S. Chung, “The Demonstration of a Physical Unclonable Function (PUF) on a Resistive-Gate FinFET Memory,” SSDM, pp. 449-450, Chiba, Japan, 2022.