執行現況與成果

前瞻單晶片三維多層級堆疊之高密度積體電路關鍵技術開發(II)

主持人

共同主持人

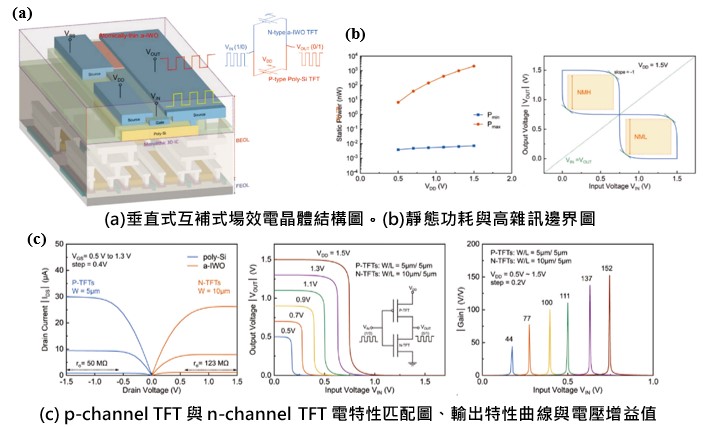

團隊成功開發出可應用於單晶片三維積體電路下的垂直式互補式場效電晶體(Complementary Field Effect Transistor, CFET),並成功以反相器邏輯電路進行驗證,相關研究之傑出研究成果,已被刊登於國際知名學術期刊“Advanced Science”中:“Heterogeneous Integration of Atomically-Thin Indium Tungsten Oxide Transistors for Low-Power Three-Dimensional Monolithic Complementary Inverter”, Advanced Science, p. 2205481, Jan., 2023. (IF: 17.52, FWCI: 3.32)。而本研究中所完成的反相器電路具有高電壓增益、低功耗,以及高雜訊邊界的特性,從反相器電路的電壓轉換曲線(VTC)中顯示出p-channel TFT與n-channel TFT兩種電晶體元件電性匹配性佳,尤其是輸出電壓增益值(Voltage gain)可以高達~ 152V/V,甚至可與單晶矽電晶體所組成的互補式反相器相匹配,且所使用的氧化銦鎢薄膜厚度只有約幾層原子層,能有效的抑制元件關閉時的漏電流路徑,使其最小靜態功耗大小只有到達幾個皮瓦特(pico-watt)遠低於矽基元件,本技術研究貢獻卓越,有望能推進半導體至下一世代。

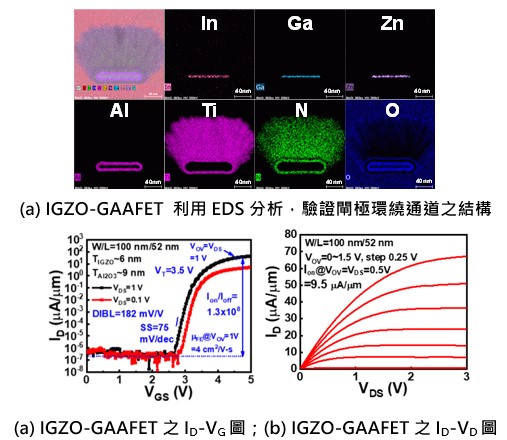

團隊率先製作出全世界第一個IGZO GAA Nanosheet電晶體,研究成果發表於2023 VLSI:“First Demonstration of a-IGZO GAA Nanosheet FETs Featuring Achievable SS=61 mV/dec, Ioff<10-7μA/μm, DIBL=44 mV/V, Positive VT, and Process Temp. of 300°C”, 2023 Symposium on VLSI Technology (VLSI), T17-3, Jun. 11-16, Japan, 2023.。本研究之元件製程溫度最高僅300℃,且通道長度可縮至52nm,具有Monolithic 3D-IC之實用潛力,此外,在Channel release的製程中,通道與犧牲層在蝕刻上擁有相當大的選擇蝕刻比。元件也展現優異之電特性,元件可操作於飽和區,S.S. 可低至75mV/dec.以下,Ion/Ioff達到至少1.3×108,且門檻電壓(VT)為正值(Enhancement mode)。

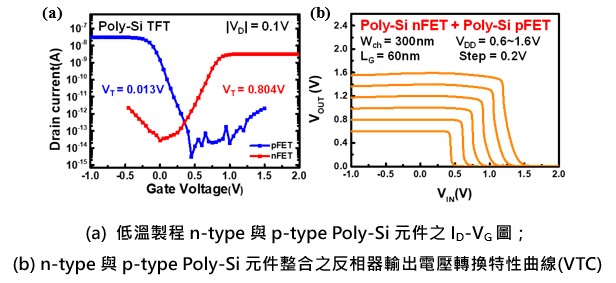

為進行高密度異質元件堆疊技術,團隊成功開發低熱預算且後段製程相容 PECVD 堆疊之複晶矽薄膜電晶體,可控制全程製程溫度在300℃以下,避免對於第一層元件影響。透過後段低溫PECVD堆疊非晶矽,製程溫度約在300℃左右,並且以低溫綠光雷射結晶,搭配介電層(inter-layer dielectric)厚度調變等,可控制熱傳導至下層元件之溫度;同時源/汲極摻雜利用微波退火進行活化,全程製程溫度皆低於300℃。本團隊已階段性完成開發n-type與p-type之PECVD Poly-Si元件,整合兩n-type與p-type元件,並實現反相器電路輸出電壓特性曲線(VTC),驗證未來於異質元件電路整合上之可行性。