執行現況與成果

應用於Å世代技術節點與低溫高效能運算之先進高密度/高性能電晶體開發、量測與模擬

主持人

共同主持人

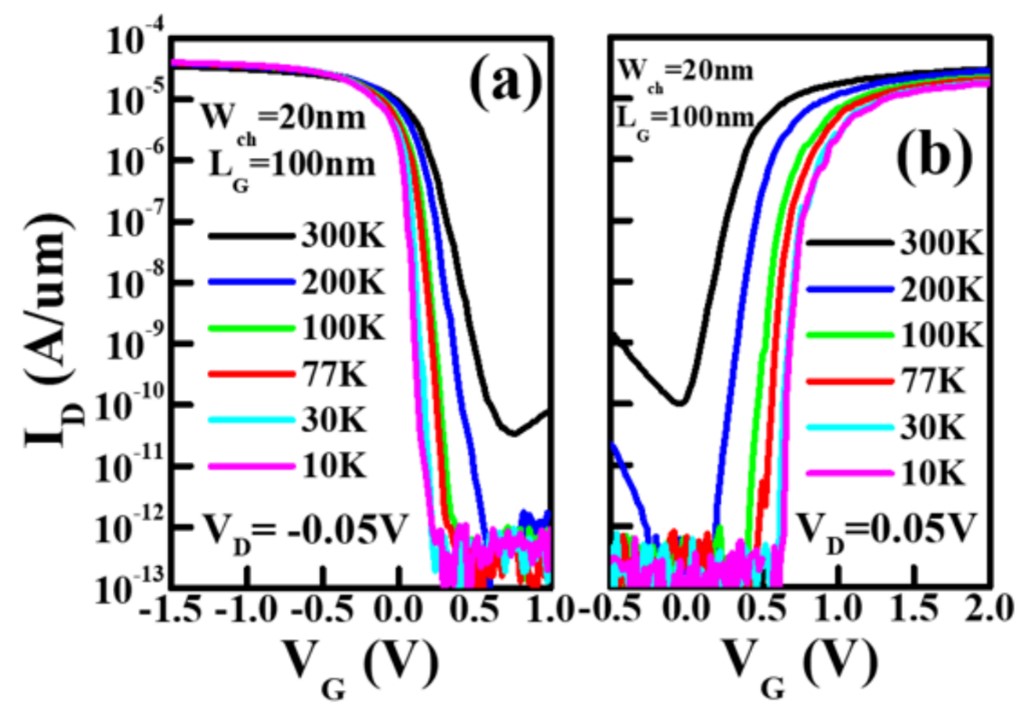

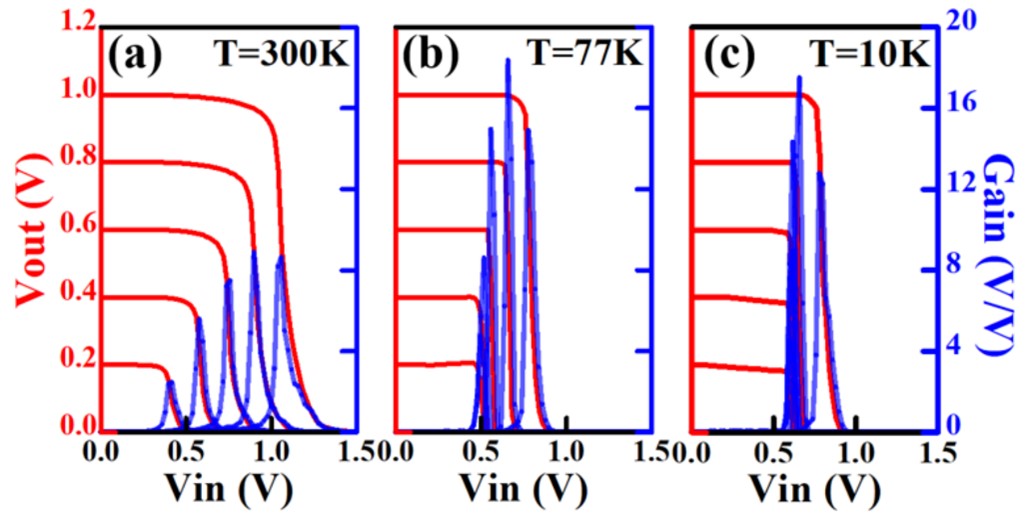

團隊在2023 IEDM會議中發表了“First Demonstration of Defect Elimination for Cryogenic Ge FinFET CMOS Inverter Showing Steep Subthreshold Slope by Using Ge-on-Insulator Structure”論文。該論文針對三種不同的鍺基先進元件進行詳細探討,並提供了從300 K到10 K的電晶體轉移特性和電路預測。研究結果表明,通過wafer bonding轉移製備GeOI FinFET可避免因磊晶成長所造成的界面缺陷,具有最佳的低溫特性。該研究提供了低溫高性能鍺基CMOS元件製備的相關技術路線。

圖一、GeOI FinFET變溫量測特性 (a) p型元件ID-VG (b) n型元件ID-VG

圖二、GeOI FinFET元件變溫電壓轉移曲線

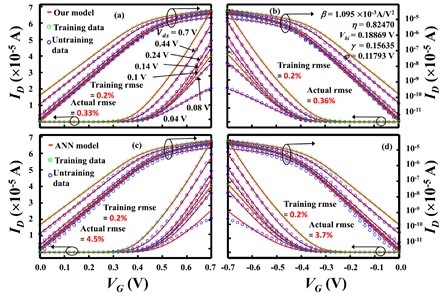

本計畫以半導體元件物理知情的深度學習模型研究垂直堆疊全閘極矽奈米片電晶體和互補式電晶體電特性,並成功用於具有千萬顆元件的SRAM晶片功率消耗估算、組合暨序向邏輯以及疊層電流鏡電路的設計與模擬。本系列研究的成果於2024年1月發表在世界權威的電子元件期刊IEEE Transactions on Electron Devices (IEEE TED);根據統計,這是台灣過去五年中,唯一以同一通訊作者和實驗室發表三篇論文在IEEE T ED期刊同一期同一卷的團隊。

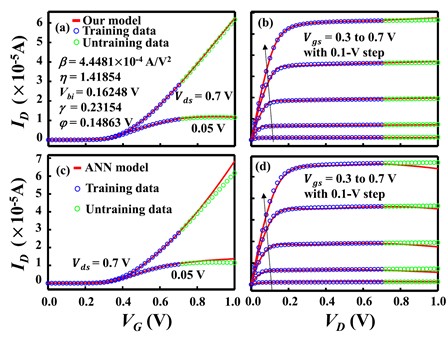

圖一、模型內的結果比較:當模型用最精簡的訓練量,訓練達到0.2%均方根誤差時,(a)(b)團隊提出的模型其整體結果誤差小於0.36%。(c)(d)文獻上[1]最新的ANN模型結果,其誤差為4.5%。

[1] C. T. Tung, M. Y. Kao, and C. Hu, “Neural network-based and modeling with high accuracy and potential model speed,” IEEE Trans. Electron Devices, vol. 69, no. 11, pp. 6476–6479, Nov. 2022.

圖二、模型外的結果比較:(a)(b)團隊提出的模型在建模外的I-V行為仍能準確地符合CFET物理。(c)(d)文獻上最新的ANN模型,在訓練範圍外其I-V行為隨偏壓增加而明顯偏離。

透過已校正到計畫所製作的鍺鰭式電晶體的TCAD模擬軟體,已能預測在低溫77K操作環境下,供應電壓可下降至0.2V,同時反相器開關切換功耗相較2031年IRDS規範已下降61%。

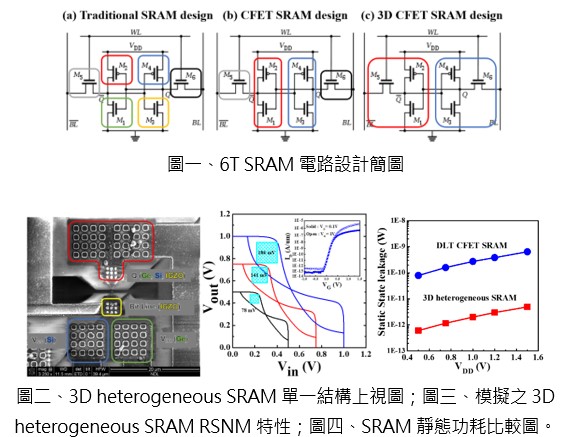

於 2022 IEDM 會議中發表了” Integration Design and Process of 3-D Heterogeneous 6T SRAM with Double Layer Transferred Ge/2Si CFET and IGZO Pass Gates for 42% Reduced Cell Size” 論文,該論文採用除透過兩次層轉移將通道數量進一步提升外,更採用後段IGZO高遷移率電晶體,將靜態隨機存取記憶體(SRAM)的PG、PU、PD堆疊於同結構上。採用該結構的記憶體相比傳統平面SRAM與CFET架構之SRAM可以更大程度的降低占地面積。其中,CFET架構之SRAM由於具備4個NMOS與2個PMOS,使得CFET結構無法更大程度的降低占地面積。基於此特點,將PG、PU、PD堆疊於同結構上,可大程度降低佔地面積外,亦使SRAM靜態功耗大幅下降。圖一為6T SRAM電路設計簡圖;圖二為3D heterogeneous SRAM單一結構上視圖;圖三為模擬之3D heterogeneous SRAM RSNM特性;圖四為SRAM靜態功耗比較圖。

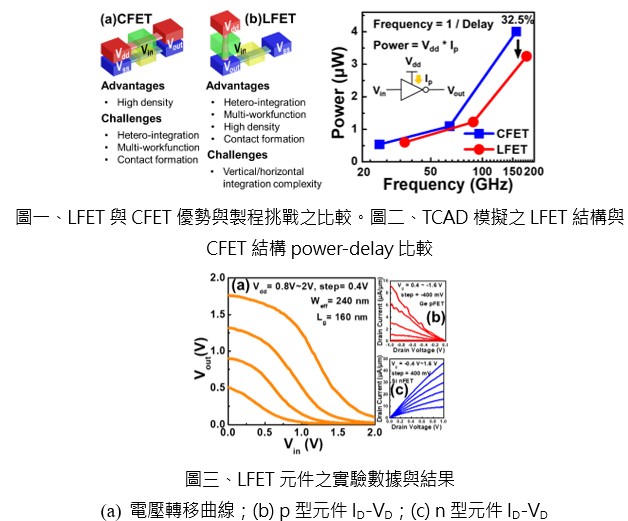

團隊首次提出結合水平電晶體與垂直電晶體的L型場效電晶體(L-shaped Field Effect Transistor, LFET),相較於互補式場效電晶體(Complementary Field Effect Transistor, CFET),LFET具有更低的能耗與更高的操作頻率,在相同操作頻率下LFET可減少32.5%能耗,在相同操作偏壓下則可以提高35%的頻率。此外,因L型結構中,垂直通道與水平通道並無上下堆疊,相較於CFET更易於分別針對n型與p型電晶體製作功函數金屬,也更容易製作接觸孔。LFET結構只需要透過磊晶就能達到異質整合,相較於CFET來說,製程上的難易度降低許多。該研究成果也發表於2022年國際電子元件會議(IEDM)。

Yang, C-Y., et al. “First Demonstration of Heterogeneous L-shaped Field Effect Transistor (LFET) for Angstrom Technology Nodes.” 2022 International Electron Devices Meeting (IEDM). IEEE, 2022.