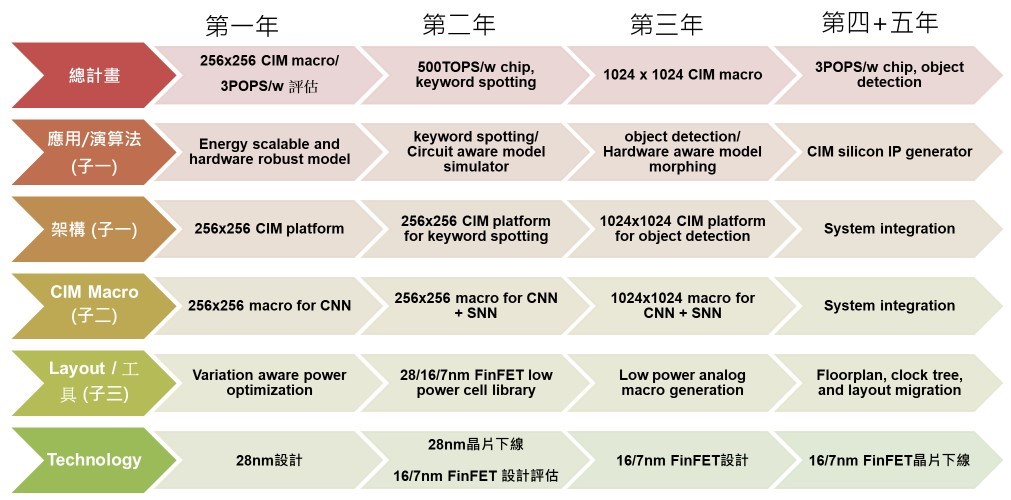

Project

Highly Energy-efficient Neuromorphic Computing System

PI

Co-PI

- Conducting the initial testing of the first AI hardware accelerator.

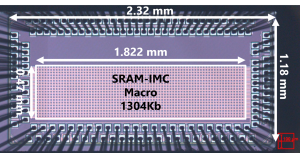

- Keyword spotting SOC had been tape-out in March 2022, using the TSMC 28HPC+ process.

- According to the computational model, expanding memory to 1.27Mb results in a 40% reduction in CIM computation latency and a 54% decrease in reading power consumption.

- Operating the memory at 0.27V can reduce CIM Macro power consumption by 40%.

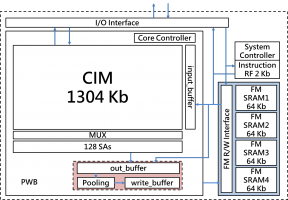

- Implementing SA sharing technology to save 80% of SA area and power consumption. Designing a testing and verification platform.

- Simultaneously designing a multi-bit output ADC array for application in CNN.

- Optimizing SNN architecture and completing the layout and verification of the neuron circuits.

- Developing TSMC 16nm FinFET low-voltage circuit layout technology while simultaneously achieving automated CIM circuit design and critical block optimization

- Using design and layout automation techniques, migrating from 28nm to 16nm CIM circuit design is expected to reduce design time from weeks to hours, maintaining the previous layout style for quick completion.

By employing CNN combined with subthreshold voltage CIM technology, we have achieved a Keyword Spotting architecture with a peak energy efficiency of up to 1551.72 TOPs/W, surpassing the initial target of 500 TOPs/W for the first stage.

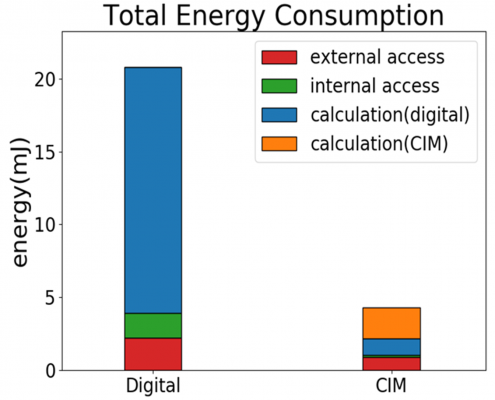

The CIM architecture consumes approximately 4.9 times less energy compared to the digital architecture. In comparison to the normal operating voltage of 0.9V, this design reduces memory leakage power by 96.4%.